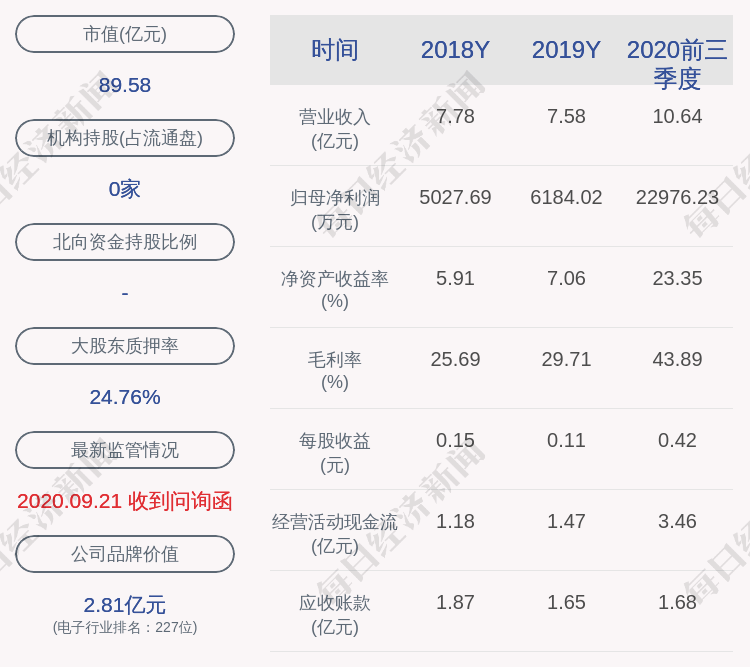

зәізұі|и®©дҪ жӣҙжё…жҘҡзҡ„дәҶи§Јзәізұіе·ҘиүәгҖҒзЎ…жҷ¶еңҶгҖҒIC

ж–Үз« еӣҫзүҮ

ж–Үз« еӣҫзүҮ

ж–Үз« еӣҫзүҮ

ж–Үз« еӣҫзүҮ

ж–Үз« еӣҫзүҮ

ж–Үз« еӣҫзүҮ

ж–Үз« еӣҫзүҮ

ж–Үз« еӣҫзүҮ

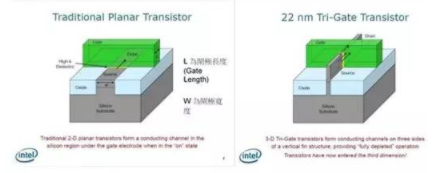

зәізұіеҲ°еә•жңүеӨҡз»Ҷеҫ®пјҹеңЁејҖе§Ӣд№ӢеүҚ пјҢ иҰҒе…ҲдәҶи§Јзәізұіз©¶з«ҹжҳҜд»Җд№Ҳж„ҸжҖқ гҖӮ еңЁж•°еӯҰдёҠ пјҢ зәізұіжҳҜ 0.000000001 зұі пјҢ дҪҶиҝҷжҳҜдёӘзӣёеҪ“е·®зҡ„дҫӢеӯҗ пјҢ жҜ•з«ҹжҲ‘们еҸӘзңӢеҫ—еҲ°е°Ҹж•°зӮ№еҗҺжңүеҫҲеӨҡдёӘйӣ¶ пјҢ еҚҙжІЎжңүе®һйҷ…зҡ„ж„ҹи§ү гҖӮ еҰӮжһңд»ҘжҢҮз”ІеҺҡеәҰеҒҡжҜ”иҫғзҡ„иҜқ пјҢ жҲ–и®ёдјҡжҜ”иҫғжҳҺжҳҫ гҖӮ з”Ёж Үе°әе®һйҷ…жөӢйҮҸзҡ„иҜқеҸҜд»Ҙеҫ—зҹҘжҢҮз”Ізҡ„еҺҡеәҰзәҰдёә 0.0001 зұіпјҲ0.1 жҜ«зұіпјү пјҢ д№ҹе°ұжҳҜиҜҙиҜ•зқҖжҠҠдёҖзүҮжҢҮз”Ізҡ„дҫ§йқўеҲҮжҲҗ 10 дёҮжқЎзәҝ пјҢ жҜҸжқЎзәҝе°ұзәҰзӯүеҗҢдәҺ 1 зәізұі пјҢ з”ұжӯӨеҸҜз•ҘдёәжғіиұЎеҫ—еҲ° 1 зәізұіжҳҜдҪ•зӯүзҡ„еҫ®е°ҸдәҶ гҖӮ зҹҘйҒ“зәізұіжңүеӨҡе°Ҹд№ӢеҗҺ пјҢ иҝҳиҰҒзҗҶи§Јзј©е°Ҹе·Ҙиүәзҡ„з”Ёж„Ҹ пјҢ зј©е°Ҹжҷ¶дҪ“з®Ўзҡ„жңҖдё»иҰҒзӣ®зҡ„ пјҢ е°ұжҳҜеҸҜд»ҘеңЁжӣҙе°Ҹзҡ„иҠҜзүҮдёӯеЎһе…ҘжӣҙеӨҡзҡ„жҷ¶дҪ“з®Ў пјҢ и®©иҠҜзүҮдёҚдјҡеӣ жҠҖжңҜжҸҗеҚҮиҖҢеҸҳеҫ—жӣҙеӨ§пјӣе…¶ж¬Ў пјҢ еҸҜд»ҘеўһеҠ еӨ„зҗҶеҷЁзҡ„иҝҗз®—ж•ҲзҺҮпјӣеҶҚиҖ… пјҢ еҮҸе°‘дҪ“з§Ҝд№ҹеҸҜд»ҘйҷҚдҪҺиҖ—з”өйҮҸпјӣжңҖеҗҺ пјҢ иҠҜзүҮдҪ“з§Ҝзј©е°ҸеҗҺ пјҢ жӣҙе®№жҳ“еЎһе…ҘиЎҢеҠЁиЈ…зҪ®дёӯ пјҢ ж»Ўи¶іжңӘжқҘиҪ»и–„еҢ–зҡ„йңҖжұӮ гҖӮ еҶҚеӣһжқҘжҺўз©¶зәізұіе·ҘиүәжҳҜд»Җд№Ҳ пјҢ д»Ҙ 14 зәізұідёәдҫӢ пјҢ е…¶е·ҘиүәжҳҜжҢҮеңЁиҠҜзүҮдёӯ пјҢ зәҝжңҖе°ҸеҸҜд»ҘеҒҡеҲ° 14 зәізұізҡ„е°әеҜё пјҢ дёӢеӣҫдёәдј з»ҹжҷ¶дҪ“з®Ўзҡ„й•ҝзӣё пјҢ д»ҘжӯӨдҪңдёәдҫӢеӯҗ гҖӮ зј©е°Ҹжҷ¶дҪ“з®Ўзҡ„жңҖдё»иҰҒзӣ®зҡ„е°ұжҳҜдёәдәҶиҰҒеҮҸе°‘иҖ—з”өйҮҸ пјҢ 然иҖҢиҰҒзј©е°Ҹе“ӘдёӘйғЁеҲҶжүҚиғҪиҫҫеҲ°иҝҷдёӘзӣ®зҡ„пјҹе·ҰдёӢеӣҫдёӯзҡ„ L е°ұжҳҜжҲ‘们жңҹжңӣзј©е°Ҹзҡ„йғЁеҲҶ гҖӮ и—үз”ұзј©е°Ҹй—ёжһҒй•ҝеәҰ пјҢ з”өжөҒеҸҜд»Ҙз”Ёжӣҙзҹӯзҡ„и·Ҝеҫ„д»Һ Drain з«ҜеҲ° Source з«ҜпјҲжңүе…ҙи¶Јзҡ„иҜқеҸҜд»ҘеҲ©з”Ё Google д»Ҙ MOSFET жҗңеҜ» пјҢ дјҡжңүжӣҙиҜҰз»Ҷзҡ„и§ЈйҮҠпјү гҖӮ

жӯӨеӨ– пјҢ и®Ўз®—жңәжҳҜд»Ҙ 0 е’Ң 1 дҪңиҝҗз®— пјҢ иҰҒеҰӮдҪ•д»Ҙжҷ¶дҪ“з®Ўж»Ўи¶іиҝҷдёӘзӣ®зҡ„е‘ўпјҹеҒҡжі•е°ұжҳҜеҲӨж–ӯжҷ¶дҪ“з®ЎжҳҜеҗҰжңүз”өжөҒжөҒйҖҡ гҖӮ еҪ“еңЁ Gate з«ҜпјҲз»ҝиүІзҡ„ж–№еқ—пјүеҒҡз”өеҺӢдҫӣз»ҷ пјҢ з”өжөҒе°ұдјҡд»Һ Drain з«ҜеҲ° Source з«Ҝ пјҢ еҰӮжһңжІЎжңүдҫӣз»ҷз”өеҺӢ пјҢ з”өжөҒе°ұдёҚдјҡжөҒеҠЁ пјҢ иҝҷж ·е°ұеҸҜд»ҘиЎЁзӨә 1 е’Ң 0 гҖӮ пјҲиҮідәҺдёәд»Җд№ҲиҰҒз”Ё 0 е’Ң 1 дҪңеҲӨж–ӯ пјҢ жңүе…ҙи¶Јзҡ„иҜқеҸҜд»ҘеҺ»жҹҘеёғе°”д»Јж•° пјҢ жҲ‘们жҳҜдҪҝз”ЁиҝҷдёӘж–№жі•дҪңжҲҗи®Ўз®—жңәзҡ„пјүе°әеҜёзј©е°Ҹжңүе…¶зү©зҗҶйҷҗеҲ¶дёҚиҝҮ пјҢ е·Ҙиүә并дёҚиғҪж— йҷҗеҲ¶зҡ„зј©е°Ҹ пјҢ еҪ“жҲ‘们е°Ҷжҷ¶дҪ“з®Ўзј©е°ҸеҲ° 20 зәізұіе·ҰеҸіж—¶ пјҢ е°ұдјҡйҒҮеҲ°йҮҸеӯҗзү©зҗҶдёӯзҡ„й—®йўҳ пјҢ и®©жҷ¶дҪ“з®ЎжңүжјҸз”өзҡ„зҺ°иұЎ пјҢ жҠөй”Җзј©е°Ҹ L ж—¶иҺ·еҫ—зҡ„ж•ҲзӣҠ гҖӮ дҪңдёәж”№е–„ж–№ејҸ пјҢ е°ұжҳҜеҜје…Ҙ FinFETпјҲTri-GateпјүиҝҷдёӘжҰӮеҝө пјҢ еҰӮеҸідёҠеӣҫ гҖӮ еңЁ Intel д»ҘеүҚжүҖеҒҡзҡ„и§ЈйҮҠдёӯ пјҢ еҸҜд»ҘзҹҘйҒ“и—үз”ұеҜје…ҘиҝҷдёӘжҠҖжңҜ пјҢ иғҪеҮҸе°‘еӣ зү©зҗҶзҺ°иұЎжүҖеҜјиҮҙзҡ„жјҸз”өзҺ°иұЎ гҖӮ жӣҙйҮҚиҰҒзҡ„жҳҜ пјҢ и—үз”ұиҝҷдёӘж–№жі•еҸҜд»ҘеўһеҠ Gate з«Ҝе’ҢдёӢеұӮзҡ„жҺҘи§Ұйқўз§Ҝ гҖӮ еңЁдј з»ҹзҡ„еҒҡжі•дёӯпјҲе·ҰдёҠеӣҫпјү пјҢ жҺҘи§ҰйқўеҸӘжңүдёҖдёӘе№ійқў пјҢ дҪҶжҳҜйҮҮз”Ё FinFETпјҲTri-GateпјүиҝҷдёӘжҠҖжңҜеҗҺ пјҢ жҺҘи§Ұйқўе°ҶеҸҳжҲҗз«ӢдҪ“ пјҢ еҸҜд»ҘиҪ»жҳ“зҡ„еўһеҠ жҺҘи§Ұйқўз§Ҝ пјҢ иҝҷж ·е°ұеҸҜд»ҘеңЁдҝқжҢҒдёҖж ·зҡ„жҺҘи§Ұйқўз§ҜдёӢи®© Source-Drain з«ҜеҸҳеҫ—жӣҙе°Ҹ пјҢ еҜ№зј©е°Ҹе°әеҜёжңүзӣёеҪ“еӨ§зҡ„её®еҠ© гҖӮ жңҖеҗҺ пјҢ еҲҷжҳҜдёәд»Җд№ҲдјҡжңүдәәиҜҙеҗ„еӨ§еҺӮиҝӣе…Ҙ 10 зәізұіеҲ¶зЁӢе°ҶйқўдёҙзӣёеҪ“дёҘеі»зҡ„жҢ‘жҲҳ пјҢ дё»еӣ жҳҜ 1 йў—еҺҹеӯҗзҡ„еӨ§е°ҸеӨ§зәҰдёә 0.1 зәізұі пјҢ еңЁ 10 зәізұізҡ„жғ…еҶөдёӢ пјҢ дёҖжқЎзәҝеҸӘжңүдёҚеҲ° 100 йў—еҺҹеӯҗ пјҢ еңЁеҲ¶дҪңдёҠзӣёеҪ“еӣ°йҡҫ пјҢ иҖҢдё”еҸӘиҰҒжңүдёҖдёӘеҺҹеӯҗзҡ„зјәйҷ· пјҢ еғҸжҳҜеңЁеҲ¶дҪңиҝҮзЁӢдёӯжңүеҺҹеӯҗжҺүеҮәжҲ–жҳҜжңүжқӮиҙЁ пјҢ е°ұдјҡдә§з”ҹдёҚзҹҘеҗҚзҡ„зҺ°иұЎ пјҢ еҪұе“Қдә§е“Ғзҡ„иүҜзҺҮ гҖӮ еҰӮжһңж— жі•жғіиұЎиҝҷдёӘйҡҫеәҰ пјҢ еҸҜд»ҘеҒҡдёӘе°Ҹе®һйӘҢ гҖӮ еңЁжЎҢдёҠз”Ё 100 дёӘе°ҸзҸ еӯҗжҺ’жҲҗдёҖдёӘ 10Г—10 зҡ„жӯЈж–№еҪў пјҢ 并且еүӘиЈҒдёҖеј зәёзӣ–еңЁзҸ еӯҗдёҠ пјҢ жҺҘзқҖз”Ёе°ҸеҲ·еӯҗжҠҠж—Ғиҫ№зҡ„зҡ„зҸ еӯҗеҲ·жҺү пјҢ жңҖеҗҺдҪҝд»–еҪўжҲҗдёҖдёӘ 10Г—5 зҡ„й•ҝж–№еҪў гҖӮ иҝҷж ·е°ұеҸҜд»ҘзҹҘйҒ“еҗ„еӨ§еҺӮжүҖйқўдёҙеҲ°зҡ„еӣ°еўғ пјҢ д»ҘеҸҠиҫҫжҲҗиҝҷдёӘзӣ®ж Ү究з«ҹжҳҜеӨҡд№Ҳиү°е·Ё гҖӮ йҡҸзқҖдёүжҳҹд»ҘеҸҠеҸ°з§Ҝз”өеңЁиҝ‘жңҹе°Ҷе®ҢжҲҗ 14 зәізұігҖҒ16 зәізұі FinFET зҡ„йҮҸдә§ пјҢ дёӨиҖ…йғҪжғідәүеӨә Apple дёӢдёҖд»Јзҡ„ iPhone иҠҜзүҮд»Је·Ҙ пјҢ жҲ‘们е°ҶзңӢеҲ°зӣёеҪ“зІҫеҪ©зҡ„е•Ҷдёҡз«һдәү пјҢ еҗҢж—¶д№ҹе°ҶиҺ·еҫ—жӣҙеҠ зңҒз”өгҖҒиҪ»и–„зҡ„жүӢжңә пјҢ иҰҒж„ҹи°ўж‘©е°”е®ҡеҫӢжүҖеёҰжқҘзҡ„еҘҪеӨ„е‘ў гҖӮ гҖҗеҚҠеҜјдҪ“科жҷ®гҖ‘еҚҠеҜјдҪ“дә§дёҡзҡ„ж №еҹәпјҡзЎ…жҷ¶еңҶжҳҜд»Җд№ҲпјҹеңЁеҚҠеҜјдҪ“зҡ„ж–°й—»дёӯ пјҢ жҖ»жҳҜдјҡжҸҗеҲ°д»Ҙе°әеҜёж ҮзӨәзҡ„жҷ¶еңҶеҺӮ пјҢ еҰӮ 8 еҗӢжҲ–жҳҜ 12 еҗӢжҷ¶еңҶеҺӮ пјҢ 然иҖҢ пјҢ жүҖи°“зҡ„жҷ¶еңҶеҲ°еә•жҳҜд»Җд№ҲдёңиҘҝпјҹе…¶дёӯ 8 еҗӢжҢҮзҡ„жҳҜд»Җд№ҲйғЁеҲҶпјҹиҰҒдә§еҮәеӨ§е°әеҜёзҡ„жҷ¶еңҶеҲ¶йҖ еҸҲжңүд»Җд№ҲйҡҫеәҰе‘ўпјҹд»ҘдёӢе°ҶйҖҗжӯҘд»Ӣз»ҚеҚҠеҜјдҪ“жңҖйҮҚиҰҒзҡ„еҹәзЎҖвҖ”вҖ”гҖҢжҷ¶еңҶгҖҚеҲ°еә•жҳҜд»Җд№Ҳ гҖӮ дҪ•и°“жҷ¶еңҶпјҹжҷ¶еңҶпјҲwaferпјү пјҢ жҳҜеҲ¶йҖ еҗ„ејҸи®Ўз®—жңәиҠҜзүҮзҡ„еҹәзЎҖ гҖӮ жҲ‘们еҸҜд»Ҙе°ҶиҠҜзүҮеҲ¶йҖ жҜ”жӢҹжҲҗз”Ёд№җй«ҳз§ҜжңЁзӣ–жҲҝеӯҗ пјҢ и—үз”ұдёҖеұӮеҸҲдёҖеұӮзҡ„е Ҷж Ҳ пјҢ е®ҢжҲҗиҮӘе·ұжңҹжңӣзҡ„йҖ еһӢпјҲд№ҹе°ұжҳҜеҗ„ејҸиҠҜзүҮпјү гҖӮ 然иҖҢ пјҢ еҰӮжһңжІЎжңүиүҜеҘҪзҡ„ең°еҹә пјҢ зӣ–еҮәжқҘзҡ„жҲҝеӯҗе°ұдјҡжӯӘжқҘжӯӘеҺ» пјҢ дёҚеҗҲиҮӘе·ұжүҖж„Ҹ пјҢ дёәдәҶеҒҡеҮәе®ҢзҫҺзҡ„жҲҝеӯҗ пјҢ дҫҝйңҖиҰҒдёҖдёӘе№ізЁізҡ„еҹәжқҝ гҖӮ еҜ№иҠҜзүҮеҲ¶йҖ жқҘиҜҙ пјҢ иҝҷдёӘеҹәжқҝе°ұжҳҜжҺҘдёӢжқҘе°ҶжҸҸиҝ°зҡ„жҷ¶еңҶ гҖӮ йҰ–е…Ҳ пјҢ е…ҲеӣһжғідёҖдёӢе°Ҹж—¶еҖҷеңЁзҺ©д№җй«ҳз§ҜжңЁж—¶ пјҢ з§ҜжңЁзҡ„иЎЁйқўйғҪдјҡжңүдёҖдёӘдёҖдёӘе°Ҹе°ҸеңҶеһӢзҡ„еҮёеҮәзү© пјҢ и—үз”ұиҝҷдёӘжһ„йҖ пјҢ жҲ‘们еҸҜе°ҶдёӨеқ—з§ҜжңЁзЁіеӣәзҡ„иҝӯеңЁдёҖиө· пјҢ дё”дёҚйңҖдҪҝз”Ёиғ¶ж°ҙ гҖӮ иҠҜзүҮеҲ¶йҖ пјҢ д№ҹжҳҜд»Ҙзұ»дјјиҝҷж ·зҡ„ж–№ејҸ пјҢ е°ҶеҗҺз»ӯж·»еҠ зҡ„еҺҹеӯҗе’Ңеҹәжқҝеӣәе®ҡеңЁдёҖиө· гҖӮ еӣ жӯӨ пјҢ жҲ‘们йңҖиҰҒеҜ»жүҫиЎЁйқўж•ҙйҪҗзҡ„еҹәжқҝ пјҢ д»Ҙж»Ўи¶іеҗҺз»ӯеҲ¶йҖ жүҖйңҖзҡ„жқЎд»¶ гҖӮ еңЁеӣәдҪ“жқҗж–ҷдёӯ пјҢ жңүдёҖз§Қзү№ж®Ҡзҡ„жҷ¶дҪ“з»“жһ„в”Җв”ҖеҚ•жҷ¶пјҲMonocrystallineпјү гҖӮ е®ғе…·жңүеҺҹеӯҗдёҖдёӘжҺҘзқҖдёҖдёӘзҙ§еҜҶжҺ’еҲ—еңЁдёҖиө·зҡ„зү№жҖ§ пјҢ еҸҜд»ҘеҪўжҲҗдёҖдёӘе№іж•ҙзҡ„еҺҹеӯҗиЎЁеұӮ гҖӮ еӣ жӯӨ пјҢ йҮҮз”ЁеҚ•жҷ¶еҒҡжҲҗжҷ¶еңҶ пјҢ дҫҝеҸҜд»Ҙж»Ўи¶ід»ҘдёҠзҡ„йңҖжұӮ гҖӮ 然иҖҢ пјҢ иҜҘеҰӮдҪ•дә§з”ҹиҝҷж ·зҡ„жқҗж–ҷе‘ў пјҢ дё»иҰҒжңүдәҢдёӘжӯҘйӘӨ пјҢ еҲҶеҲ«дёәзәҜеҢ–д»ҘеҸҠжӢүжҷ¶ пјҢ д№ӢеҗҺдҫҝиғҪе®ҢжҲҗиҝҷж ·зҡ„жқҗж–ҷ гҖӮ еҰӮдҪ•еҲ¶йҖ еҚ•жҷ¶зҡ„жҷ¶еңҶзәҜеҢ–еҲҶжҲҗдёӨдёӘйҳ¶ж®ө пјҢ 第дёҖжӯҘжҳҜеҶ¶йҮ‘зә§зәҜеҢ– пјҢ жӯӨдёҖиҝҮзЁӢдё»иҰҒжҳҜеҠ е…Ҙзўі пјҢ д»Ҙж°§еҢ–иҝҳеҺҹзҡ„ж–№ејҸ пјҢ е°Ҷж°§еҢ–зЎ…иҪ¬жҚўжҲҗ 98% д»ҘдёҠзәҜеәҰзҡ„зЎ… гҖӮ еӨ§йғЁд»Ҫзҡ„йҮ‘еұһжҸҗзӮј пјҢ еғҸжҳҜй“ҒжҲ–й“ңзӯүйҮ‘еұһ пјҢ зҡҶжҳҜйҮҮз”Ёиҝҷж ·зҡ„ж–№ејҸиҺ·еҫ—и¶іеӨҹзәҜеәҰзҡ„йҮ‘еұһ гҖӮ дҪҶжҳҜ пјҢ 98% еҜ№дәҺиҠҜзүҮеҲ¶йҖ жқҘиҜҙдҫқж—§дёҚеӨҹ пјҢ д»ҚйңҖиҰҒиҝӣдёҖжӯҘжҸҗеҚҮ гҖӮ еӣ жӯӨ пјҢ е°ҶеҶҚиҝӣдёҖжӯҘйҮҮз”ЁиҘҝй—ЁеӯҗеҲ¶зЁӢпјҲSiemens processпјүдҪңзәҜеҢ– пјҢ еҰӮжӯӨ пјҢ е°ҶиҺ·еҫ—еҚҠеҜјдҪ“еҲ¶зЁӢжүҖйңҖзҡ„й«ҳзәҜеәҰеӨҡжҷ¶зЎ… гҖӮ

в–ІзЎ…жҹұеҲ¶йҖ жөҒзЁӢпјҲSource: WikipediaпјүжҺҘзқҖ пјҢ е°ұжҳҜжӢүжҷ¶зҡ„жӯҘйӘӨ гҖӮ йҰ–е…Ҳ пјҢ е°ҶеүҚйқўжүҖиҺ·еҫ—зҡ„й«ҳзәҜеәҰеӨҡжҷ¶зЎ…иһҚеҢ– пјҢ еҪўжҲҗж¶ІжҖҒзҡ„зЎ… гҖӮ д№ӢеҗҺ пјҢ д»ҘеҚ•жҷ¶зҡ„зЎ…з§ҚпјҲseedпјүе’Ңж¶ІдҪ“иЎЁйқўжҺҘи§Ұ пјҢ дёҖиҫ№ж—ӢиҪ¬дёҖиҫ№зј“ж…ўзҡ„еҗ‘дёҠжӢүиө· гҖӮ иҮідәҺдёәдҪ•йңҖиҰҒеҚ•жҷ¶зҡ„зЎ…з§Қ пјҢ жҳҜеӣ дёәзЎ…еҺҹеӯҗжҺ’еҲ—е°ұе’ҢдәәжҺ’йҳҹдёҖж · пјҢ дјҡйңҖиҰҒжҺ’еӨҙи®©еҗҺжқҘзҡ„дәәиҜҘеҰӮдҪ•жӯЈзЎ®зҡ„жҺ’еҲ— пјҢ зЎ…з§ҚдҫҝжҳҜйҮҚиҰҒзҡ„жҺ’еӨҙ пјҢ и®©еҗҺжқҘзҡ„еҺҹеӯҗзҹҘйҒ“иҜҘеҰӮдҪ•жҺ’йҳҹ гҖӮ жңҖеҗҺ пјҢ еҫ…зҰ»ејҖж¶Ійқўзҡ„зЎ…еҺҹеӯҗеҮқеӣәеҗҺ пјҢ жҺ’еҲ—ж•ҙйҪҗзҡ„еҚ•жҷ¶зЎ…жҹұдҫҝе®ҢжҲҗдәҶ гҖӮ

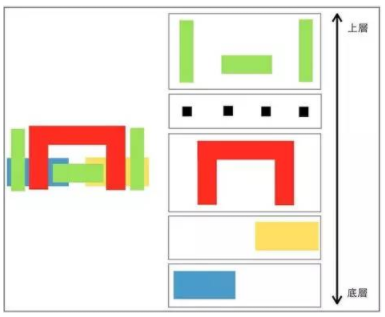

еҚ•жҷ¶зЎ…жҹұпјҲSouseпјҡWikipediaпјү然иҖҢ пјҢ 8еҗӢгҖҒ12еҗӢеҸҲд»ЈиЎЁд»Җд№ҲдёңиҘҝе‘ўпјҹд»–жҢҮзҡ„жҳҜжҲ‘们дә§з”ҹзҡ„жҷ¶жҹұ пјҢ й•ҝеҫ—еғҸ铅笔笔жқҶзҡ„йғЁеҲҶ пјҢ иЎЁйқўз»ҸиҝҮеӨ„зҗҶ并еҲҮжҲҗи–„еңҶзүҮеҗҺзҡ„зӣҙеҫ„ гҖӮ иҮідәҺеҲ¶йҖ еӨ§е°әеҜёжҷ¶еңҶеҸҲжңүд»Җд№ҲйҡҫеәҰе‘ўпјҹеҰӮеүҚйқўжүҖиҜҙ пјҢ жҷ¶жҹұзҡ„еҲ¶дҪңиҝҮзЁӢе°ұеғҸжҳҜеңЁеҒҡжЈүиҠұзі–дёҖж · пјҢ дёҖиҫ№ж—ӢиҪ¬дёҖиҫ№жҲҗеһӢ гҖӮ жңүеҲ¶дҪңиҝҮжЈүиҠұзі–зҡ„иҜқ пјҢ еә”иҜҘйғҪзҹҘйҒ“иҰҒеҒҡеҮәеӨ§иҖҢдё”жүҺе®һзҡ„жЈүиҠұзі–жҳҜзӣёеҪ“еӣ°йҡҫзҡ„ пјҢ иҖҢжӢүжҷ¶зҡ„иҝҮзЁӢд№ҹжҳҜдёҖж · пјҢ ж—ӢиҪ¬жӢүиө·зҡ„йҖҹеәҰд»ҘеҸҠжё©еәҰзҡ„жҺ§еҲ¶йғҪдјҡеҪұе“ҚеҲ°жҷ¶жҹұзҡ„иҙЁйҮҸ гҖӮ д№ҹеӣ жӯӨ пјҢ е°әеҜёж„ҲеӨ§ж—¶ пјҢ жӢүжҷ¶еҜ№йҖҹеәҰдёҺжё©еәҰзҡ„иҰҒжұӮе°ұжӣҙй«ҳ пјҢ еӣ жӯӨиҰҒеҒҡеҮәй«ҳиҙЁйҮҸ 12 еҗӢжҷ¶еңҶзҡ„йҡҫеәҰе°ұжҜ” 8 еҗӢжҷ¶еңҶиҝҳжқҘеҫ—й«ҳ гҖӮ еҸӘжҳҜ пјҢ дёҖж•ҙжқЎзҡ„зЎ…жҹұе№¶ж— жі•еҒҡжҲҗиҠҜзүҮеҲ¶йҖ зҡ„еҹәжқҝ пјҢ дёәдәҶдә§з”ҹдёҖзүҮдёҖзүҮзҡ„зЎ…жҷ¶еңҶ пјҢ жҺҘзқҖйңҖиҰҒд»Ҙй’»зҹіеҲҖе°ҶзЎ…жҷ¶жҹұжЁӘеҗ‘еҲҮжҲҗеңҶзүҮ пјҢ еңҶзүҮеҶҚз»Ҹз”ұжҠӣе…үдҫҝеҸҜеҪўжҲҗиҠҜзүҮеҲ¶йҖ жүҖйңҖзҡ„зЎ…жҷ¶еңҶ гҖӮ з»ҸиҝҮиҝҷд№ҲеӨҡжӯҘйӘӨ пјҢ иҠҜзүҮеҹәжқҝзҡ„еҲ¶йҖ дҫҝеӨ§еҠҹе‘ҠжҲҗ пјҢ дёӢдёҖжӯҘдҫҝжҳҜе Ҷж ҲжҲҝеӯҗзҡ„жӯҘйӘӨ пјҢ д№ҹе°ұжҳҜиҠҜзүҮеҲ¶йҖ гҖӮ иҮідәҺиҜҘеҰӮдҪ•еҲ¶дҪңиҠҜзүҮе‘ўпјҹжҺҘзқҖеҫҖдёӢзңӢ гҖӮ гҖҗеҚҠеҜјдҪ“科жҷ®гҖ‘IC иҠҜзүҮзҡ„еҲ¶йҖ пјҢ еұӮеұӮжү“йҖ зҡ„й«ҳ科жҠҖе·ҘиүәеңЁд»Ӣз»ҚиҝҮзЎ…жҷ¶еңҶжҳҜд»Җд№ҲдёңиҘҝеҗҺ пјҢ еҗҢж—¶ пјҢ д№ҹзҹҘйҒ“еҲ¶йҖ IC иҠҜзүҮе°ұеғҸжҳҜз”Ёд№җй«ҳз§ҜжңЁзӣ–жҲҝеӯҗдёҖж · пјҢ и—үз”ұдёҖеұӮеҸҲдёҖеұӮзҡ„е Ҷж Ҳ пјҢ еҲӣйҖ иҮӘе·ұжүҖжңҹжңӣзҡ„йҖ еһӢ гҖӮ 然иҖҢ пјҢ зӣ–жҲҝеӯҗжңүзӣёеҪ“еӨҡзҡ„жӯҘйӘӨ пјҢ IC еҲ¶йҖ д№ҹжҳҜдёҖж · пјҢ еҲ¶йҖ IC 究з«ҹжңүе“ӘдәӣжӯҘйӘӨпјҹжң¬ж–Үе°Ҷе°Ҷе°ұ IC иҠҜзүҮеҲ¶йҖ зҡ„жөҒзЁӢеҒҡд»Ӣз»Қ гҖӮ еұӮеұӮе Ҷж Ҳзҡ„иҠҜзүҮжһ¶жһ„еңЁејҖе§ӢеүҚ пјҢ жҲ‘们иҰҒе…Ҳи®ӨиҜҶ IC иҠҜзүҮжҳҜд»Җд№Ҳ гҖӮ IC пјҢ е…ЁеҗҚйӣҶжҲҗз”өи·ҜпјҲIntegrated Circuitпјү пјҢ з”ұе®ғзҡ„е‘ҪеҗҚеҸҜзҹҘе®ғжҳҜе°Ҷи®ҫи®ЎеҘҪзҡ„з”өи·Ҝ пјҢ д»Ҙе Ҷж Ҳзҡ„ж–№ејҸз»„еҗҲиө·жқҘ гҖӮ и—үз”ұиҝҷдёӘж–№жі• пјҢ жҲ‘们еҸҜд»ҘеҮҸе°‘иҝһжҺҘз”өи·Ҝж—¶жүҖйңҖиҖ—иҙ№зҡ„йқўз§Ҝ гҖӮ дёӢеӣҫдёә IC з”өи·Ҝзҡ„ 3D еӣҫ пјҢ д»ҺеӣҫдёӯеҸҜд»ҘзңӢеҮәе®ғзҡ„з»“жһ„е°ұеғҸжҲҝеӯҗзҡ„жўҒе’Ңжҹұ пјҢ дёҖеұӮдёҖеұӮе Ҷж Ҳ пјҢ иҝҷд№ҹе°ұжҳҜдёәдҪ•дјҡе°Ҷ IC еҲ¶йҖ жҜ”жӢҹжҲҗзӣ–жҲҝеӯҗ гҖӮ

в–І IC иҠҜзүҮзҡ„ 3D еү–йқўеӣҫ гҖӮ д»ҺдёҠеӣҫдёӯ IC иҠҜзүҮзҡ„ 3D еү–йқўеӣҫжқҘзңӢ пјҢ еә•йғЁж·ұи“қиүІзҡ„йғЁеҲҶе°ұжҳҜдёҠдёҖзҜҮд»Ӣз»Қзҡ„жҷ¶еңҶ пјҢ д»Һиҝҷеј еӣҫеҸҜд»ҘжӣҙжҳҺзЎ®зҡ„зҹҘйҒ“ пјҢ жҷ¶еңҶеҹәжқҝеңЁиҠҜзүҮдёӯжү®жј”зҡ„и§’иүІжҳҜдҪ•зӯүйҮҚиҰҒ гҖӮ иҮідәҺзәўиүІд»ҘеҸҠеңҹй»„иүІзҡ„йғЁеҲҶ пјҢ еҲҷжҳҜдәҺ IC еҲ¶дҪңж—¶иҰҒе®ҢжҲҗзҡ„ең°ж–№ гҖӮ йҰ–е…Ҳ пјҢ еңЁиҝҷйҮҢеҸҜд»Ҙе°ҶзәўиүІзҡ„йғЁеҲҶжҜ”жӢҹжҲҗй«ҳжҘјдёӯзҡ„дёҖжҘјеӨ§еҺ… гҖӮ дёҖжҘјеӨ§еҺ… пјҢ жҳҜдёҖж ӢжҲҝеӯҗзҡ„й—ЁжҲ· пјҢ еҮәе…ҘйғҪз”ұиҝҷйҮҢ пјҢ еңЁжҺҢжҸЎдәӨйҖҡдёӢйҖҡеёёдјҡжңүиҫғеӨҡзҡ„жңәиғҪжҖ§ гҖӮ еӣ жӯӨ пјҢ е’Ңе…¶д»–жҘјеұӮзӣёжҜ” пјҢ еңЁе…ҙе»әж—¶дјҡжҜ”иҫғеӨҚжқӮ пјҢ йңҖиҰҒиҫғеӨҡзҡ„жӯҘйӘӨ гҖӮ еңЁ IC з”өи·Ҝдёӯ пјҢ иҝҷдёӘеӨ§еҺ…е°ұжҳҜйҖ»иҫ‘й—ёеұӮ пјҢ е®ғжҳҜж•ҙйў— IC дёӯжңҖйҮҚиҰҒзҡ„йғЁеҲҶ пјҢ и—үз”ұе°ҶеӨҡз§ҚйҖ»иҫ‘й—ёз»„еҗҲеңЁдёҖиө· пјҢ е®ҢжҲҗеҠҹиғҪйҪҗе…Ёзҡ„ IC иҠҜзүҮ гҖӮ й»„иүІзҡ„йғЁеҲҶ пјҢ еҲҷеғҸжҳҜдёҖиҲ¬зҡ„жҘјеұӮ гҖӮ е’ҢдёҖжҘјзӣёжҜ” пјҢ дёҚдјҡжңүеӨӘеӨҚжқӮзҡ„жһ„йҖ пјҢ иҖҢдё”жҜҸеұӮжҘјеңЁе…ҙе»әж—¶д№ҹдёҚдјҡжңүеӨӘеӨҡеҸҳеҢ– гҖӮ иҝҷдёҖеұӮзҡ„зӣ®зҡ„ пјҢ жҳҜе°ҶзәўиүІйғЁеҲҶзҡ„йҖ»иҫ‘й—ёзӣёиҝһеңЁдёҖиө· гҖӮ д№ӢжүҖд»ҘйңҖиҰҒиҝҷд№ҲеӨҡеұӮ пјҢ жҳҜеӣ дёәжңүеӨӘеӨҡзәҝи·ҜиҰҒиҝһз»“еңЁдёҖиө· пјҢ еңЁеҚ•еұӮж— жі•е®№зәіжүҖжңүзҡ„зәҝи·ҜдёӢ пјҢ е°ұиҰҒеӨҡиҝӯеҮ еұӮжқҘиҫҫжҲҗиҝҷдёӘзӣ®ж ҮдәҶ гҖӮ еңЁиҝҷд№Ӣдёӯ пјҢ дёҚеҗҢеұӮзҡ„зәҝи·ҜдјҡдёҠдёӢзӣёиҝһд»Ҙж»Ўи¶іжҺҘзәҝзҡ„йңҖжұӮ гҖӮ еҲҶеұӮж–Ҫе·Ҙ пјҢ йҖҗеұӮжһ¶жһ„зҹҘйҒ“ IC зҡ„жһ„йҖ еҗҺ пјҢ жҺҘдёӢжқҘиҰҒд»Ӣз»ҚиҜҘеҰӮдҪ•еҲ¶дҪң гҖӮ иҜ•жғідёҖдёӢ пјҢ еҰӮжһңиҰҒд»ҘжІ№жјҶе–·зҪҗеҒҡзІҫз»ҶдҪңеӣҫж—¶ пјҢ жҲ‘们йңҖе…ҲеүІеҮәеӣҫеҪўзҡ„йҒ®зӣ–жқҝ пјҢ зӣ–еңЁзәёдёҠ гҖӮ жҺҘзқҖеҶҚе°ҶжІ№жјҶеқҮеҢҖең°е–·еңЁзәёдёҠ пјҢ еҫ…жІ№жјҶе№ІеҗҺ пјҢ еҶҚе°ҶйҒ®жқҝжӢҝејҖ гҖӮ дёҚж–ӯзҡ„йҮҚеӨҚиҝҷдёӘжӯҘйӘӨеҗҺ пјҢ дҫҝеҸҜе®ҢжҲҗж•ҙйҪҗдё”еӨҚжқӮзҡ„еӣҫеҪў гҖӮ еҲ¶йҖ IC е°ұжҳҜд»Ҙзұ»дјјзҡ„ж–№ејҸ пјҢ и—үз”ұйҒ®зӣ–зҡ„ж–№ејҸдёҖеұӮдёҖеұӮзҡ„е Ҷж Ҳиө·жқҘ гҖӮ

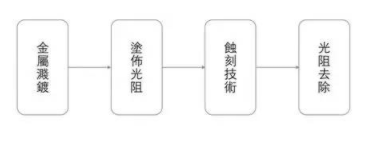

еҲ¶дҪң IC ж—¶ пјҢ еҸҜд»Ҙз®ҖеҚ•еҲҶжҲҗд»ҘдёҠ 4 з§ҚжӯҘйӘӨ гҖӮ иҷҪ然е®һйҷ…еҲ¶йҖ ж—¶ пјҢ еҲ¶йҖ зҡ„жӯҘйӘӨдјҡжңүе·®ејӮ пјҢ дҪҝз”Ёзҡ„жқҗж–ҷд№ҹжңүжүҖдёҚеҗҢ пјҢ дҪҶжҳҜеӨ§дҪ“дёҠзҡҶйҮҮз”Ёзұ»дјјзҡ„еҺҹзҗҶ гҖӮ иҝҷдёӘжөҒзЁӢе’ҢжІ№жјҶдҪңз”»жңүдәӣи®ёдёҚеҗҢ пјҢ IC еҲ¶йҖ жҳҜе…Ҳж¶Ӯж–ҷеҶҚеҠ еҒҡйҒ®зӣ– пјҢ жІ№жјҶдҪңз”»еҲҷжҳҜе…ҲйҒ®зӣ–еҶҚдҪңз”» гҖӮ д»ҘдёӢе°Ҷд»Ӣз»Қеҗ„жөҒзЁӢ гҖӮ 1.йҮ‘еұһжә…й•Җпјҡе°Ҷж¬ІдҪҝз”Ёзҡ„йҮ‘еұһжқҗж–ҷеқҮеҢҖжҙ’еңЁжҷ¶еңҶзүҮдёҠ пјҢ еҪўжҲҗдёҖи–„иҶң гҖӮ 2.ж¶Ӯеёғе…үйҳ»пјҡе…Ҳе°Ҷе…үйҳ»жқҗж–ҷж”ҫеңЁжҷ¶еңҶзүҮдёҠ пјҢ йҖҸиҝҮе…үзҪ©пјҲе…үзҪ©еҺҹзҗҶз•ҷеҫ…дёӢж¬ЎиҜҙжҳҺпјү пјҢ е°Ҷе…үжқҹжү“еңЁдёҚиҰҒзҡ„йғЁеҲҶдёҠ пјҢ з ҙеқҸе…үйҳ»жқҗж–ҷз»“жһ„ гҖӮ жҺҘзқҖ пјҢ еҶҚд»ҘеҢ–еӯҰиҚҜеүӮе°Ҷиў«з ҙеқҸзҡ„жқҗж–ҷжҙ—еҺ» гҖӮ 3.иҡҖеҲ»жҠҖжңҜпјҡе°ҶжІЎжңүеҸ—е…үйҳ»дҝқжҠӨзҡ„зЎ…жҷ¶еңҶ пјҢ д»ҘзҰ»еӯҗжқҹиҡҖеҲ» гҖӮ 4.е…үйҳ»еҺ»йҷӨпјҡдҪҝз”ЁеҺ»е…үйҳ»ж¶ІзҡҶеү©дёӢзҡ„е…үйҳ»жә¶и§ЈжҺү пјҢ еҰӮжӯӨдҫҝе®ҢжҲҗдёҖж¬ЎжөҒзЁӢ гҖӮ жңҖеҗҺдҫҝдјҡеңЁдёҖж•ҙзүҮжҷ¶еңҶдёҠе®ҢжҲҗеҫҲеӨҡ IC иҠҜзүҮ пјҢ жҺҘдёӢжқҘеҸӘиҰҒе°Ҷе®ҢжҲҗзҡ„ж–№еҪў IC иҠҜзүҮеүӘдёӢ пјҢ дҫҝеҸҜйҖҒеҲ°е°ҒиЈ…еҺӮеҒҡе°ҒиЈ… пјҢ иҮідәҺе°ҒиЈ…еҺӮжҳҜд»Җд№ҲдёңиҘҝпјҹе°ұиҰҒеҫ…д№ӢеҗҺеҶҚеҒҡиҜҙжҳҺе•° гҖӮ

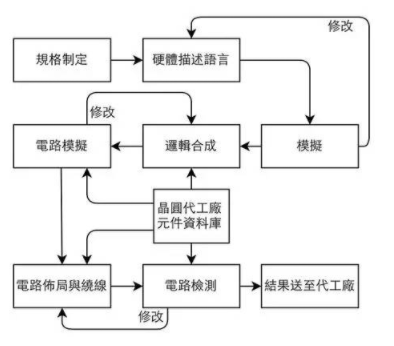

в–І еҗ„з§Қе°әеҜёжҷ¶еңҶзҡ„жҜ”иҫғ гҖӮ пјҲSourceпјҡWikipediaпјүгҖҗеҚҠеҜјдҪ“科жҷ®гҖ‘IC еҠҹиғҪзҡ„е…ій”® пјҢ еӨҚжқӮз№Ғзҗҗзҡ„иҠҜзүҮи®ҫи®ЎжөҒзЁӢеңЁеүҚйқўе·Із»Ҹд»Ӣз»ҚиҝҮиҠҜзүҮеҲ¶йҖ зҡ„иҝҮзЁӢе°ұеҰӮеҗҢз”Ёд№җй«ҳзӣ–жҲҝеӯҗдёҖж · пјҢ е…Ҳжңүжҷ¶еңҶдҪңдёәең°еҹә пјҢ еҶҚеұӮеұӮеҫҖдёҠиҝӯзҡ„иҠҜзүҮеҲ¶йҖ жөҒзЁӢеҗҺ пјҢ е°ұеҸҜдә§еҮәеҝ…иҰҒзҡ„ IC иҠҜзүҮ гҖӮ 然иҖҢ пјҢ жІЎжңүи®ҫи®Ўеӣҫ пјҢ жӢҘжңүеҶҚејәеҲ¶йҖ иғҪеҠӣйғҪжІЎжңүз”Ё пјҢ еӣ жӯӨ пјҢ е»әзӯ‘еёҲзҡ„и§’иүІзӣёеҪ“йҮҚиҰҒ гҖӮ дҪҶжҳҜ IC и®ҫи®Ўдёӯзҡ„е»әзӯ‘еёҲ究з«ҹжҳҜи°Ғе‘ўпјҹжҺҘдёӢжқҘиҰҒй’ҲеҜ№ IC и®ҫи®ЎеҒҡд»Ӣз»Қ гҖӮ еңЁ IC з”ҹдә§жөҒзЁӢдёӯ пјҢ IC еӨҡз”ұдё“дёҡ IC и®ҫи®Ўе…¬еҸёиҝӣиЎҢ规еҲ’гҖҒи®ҫи®Ў пјҢ еғҸжҳҜиҒ”еҸ‘科гҖҒй«ҳйҖҡгҖҒIntel зӯүзҹҘеҗҚеӨ§еҺӮ пјҢ йғҪиҮӘиЎҢи®ҫи®Ўеҗ„иҮӘзҡ„ IC иҠҜзүҮ пјҢ жҸҗдҫӣдёҚеҗҢи§„ж јгҖҒж•ҲиғҪзҡ„иҠҜзүҮз»ҷдёӢжёёеҺӮе•ҶйҖүжӢ© гҖӮ еӣ дёә IC жҳҜз”ұеҗ„еҺӮиҮӘиЎҢи®ҫи®Ў пјҢ жүҖд»Ҙ IC и®ҫи®ЎеҚҒеҲҶд»°иө–е·ҘзЁӢеёҲзҡ„жҠҖжңҜ пјҢ е·ҘзЁӢеёҲзҡ„зҙ иҙЁеҪұе“ҚзқҖдёҖй—ҙдјҒдёҡзҡ„д»·еҖј гҖӮ 然иҖҢ пјҢ е·ҘзЁӢеёҲ们еңЁи®ҫи®ЎдёҖйў— IC иҠҜзүҮж—¶ пјҢ 究з«ҹжңүйӮЈдәӣжӯҘйӘӨпјҹи®ҫи®ЎжөҒзЁӢеҸҜд»Ҙз®ҖеҚ•еҲҶжҲҗеҰӮдёӢ гҖӮ

и®ҫ计第дёҖжӯҘ пјҢ и®ўе®ҡзӣ®ж ҮеңЁ IC и®ҫи®Ўдёӯ пјҢ жңҖйҮҚиҰҒзҡ„жӯҘйӘӨе°ұжҳҜи§„ж јеҲ¶е®ҡ гҖӮ иҝҷдёӘжӯҘйӘӨе°ұеғҸжҳҜеңЁи®ҫи®Ўе»әзӯ‘еүҚ пјҢ е…ҲеҶіе®ҡиҰҒеҮ й—ҙжҲҝй—ҙгҖҒжөҙе®Ө пјҢ жңүд»Җд№Ҳе»әзӯ‘法规йңҖиҰҒйҒөе®Ҳ пјҢ еңЁзЎ®е®ҡеҘҪжүҖжңүзҡ„еҠҹиғҪд№ӢеҗҺеңЁиҝӣиЎҢи®ҫи®Ў пјҢ иҝҷж ·жүҚдёҚз”ЁеҶҚиҠұйўқеӨ–зҡ„ж—¶й—ҙиҝӣиЎҢеҗҺз»ӯдҝ®ж”№ гҖӮ IC и®ҫи®Ўд№ҹйңҖиҰҒз»ҸиҝҮзұ»дјјзҡ„жӯҘйӘӨ пјҢ жүҚиғҪзЎ®дҝқи®ҫи®ЎеҮәжқҘзҡ„иҠҜзүҮдёҚдјҡжңүд»»дҪ•е·®й”ҷ гҖӮ и§„ж јеҲ¶е®ҡзҡ„第дёҖжӯҘдҫҝжҳҜзЎ®е®ҡ IC зҡ„зӣ®зҡ„гҖҒж•ҲиғҪдёәдҪ• пјҢ еҜ№еӨ§ж–№еҗ‘еҒҡи®ҫе®ҡ гҖӮ жҺҘзқҖжҳҜеҜҹзңӢжңүе“ӘдәӣеҚҸи®®иҰҒз¬ҰеҗҲ пјҢ еғҸж— зәҝзҪ‘еҚЎзҡ„иҠҜзүҮе°ұйңҖиҰҒз¬ҰеҗҲ IEEE 802.11 зӯү规иҢғ пјҢ дёҚ然 пјҢ иҝҷиҠҜзүҮе°Ҷж— жі•е’ҢеёӮйқўдёҠзҡ„дә§е“Ғе…је®№ пјҢ дҪҝе®ғж— жі•е’Ңе…¶д»–и®ҫеӨҮиҒ”жңә гҖӮ жңҖеҗҺеҲҷжҳҜзЎ®з«Ӣиҝҷйў— IC зҡ„е®һдҪңж–№жі• пјҢ е°ҶдёҚеҗҢеҠҹиғҪеҲҶй…ҚжҲҗдёҚеҗҢзҡ„еҚ•е…ғ пјҢ 并确з«ӢдёҚеҗҢеҚ•е…ғй—ҙй“ҫжҺҘзҡ„ж–№жі• пјҢ еҰӮжӯӨдҫҝе®ҢжҲҗи§„ж јзҡ„еҲ¶е®ҡ гҖӮ и®ҫи®Ўе®Ңи§„ж јеҗҺ пјҢ жҺҘзқҖе°ұжҳҜи®ҫи®ЎиҠҜзүҮзҡ„з»ҶиҠӮдәҶ гҖӮ иҝҷдёӘжӯҘйӘӨе°ұеғҸеҲқжӯҘи®°дёӢе»әзӯ‘зҡ„规画 пјҢ е°Ҷж•ҙдҪ“иҪ®е»“жҸҸз»ҳеҮәжқҘ пјҢ ж–№дҫҝеҗҺз»ӯеҲ¶еӣҫ гҖӮ еңЁ IC иҠҜзүҮдёӯ пјҢ дҫҝжҳҜдҪҝ用硬件жҸҸиҝ°иҜӯиЁҖпјҲHDLпјүе°Ҷз”өи·ҜжҸҸеҶҷеҮәжқҘ гҖӮ еёёдҪҝз”Ёзҡ„ HDL жңү VerilogгҖҒVHDL зӯү пјҢ и—үз”ұзЁӢеәҸд»Јз ҒдҫҝеҸҜиҪ»жҳ“ең°е°ҶдёҖйў— IC ең°иҸңеҚ•иҫҫеҮәжқҘ гҖӮ жҺҘзқҖе°ұжҳҜжЈҖжҹҘзЁӢеәҸеҠҹиғҪзҡ„жӯЈзЎ®жҖ§е№¶жҢҒз»ӯдҝ®ж”№ пјҢ зӣҙеҲ°е®ғж»Ўи¶іжңҹжңӣзҡ„еҠҹиғҪдёәжӯў гҖӮ

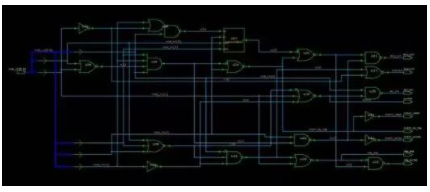

в–І 32 bits еҠ жі•еҷЁзҡ„ Verilog иҢғдҫӢ гҖӮ жңүдәҶи®Ўз®—жңә пјҢ дәӢжғ…йғҪеҸҳеҫ—е®№жҳ“жңүдәҶе®Ңж•ҙ规画еҗҺ пјҢ жҺҘдёӢжқҘдҫҝжҳҜз”»еҮәе№ійқўзҡ„и®ҫи®Ўи“қеӣҫ гҖӮ еңЁ IC и®ҫи®Ўдёӯ пјҢ йҖ»иҫ‘еҗҲжҲҗиҝҷдёӘжӯҘйӘӨдҫҝжҳҜе°ҶзЎ®е®ҡж— иҜҜзҡ„ HDL code пјҢ ж”ҫе…Ҙз”өеӯҗи®ҫи®ЎиҮӘеҠЁеҢ–е·Ҙе…·пјҲEDA toolпјү пјҢ и®©и®Ўз®—жңәе°Ҷ HDL code иҪ¬жҚўжҲҗйҖ»иҫ‘з”өи·Ҝ пјҢ дә§з”ҹеҰӮдёӢзҡ„з”өи·Ҝеӣҫ гҖӮ д№ӢеҗҺ пјҢ еҸҚеӨҚзҡ„зЎ®е®ҡжӯӨйҖ»иҫ‘й—ёи®ҫи®ЎеӣҫжҳҜеҗҰз¬ҰеҗҲи§„ж је№¶дҝ®ж”№ пјҢ зӣҙеҲ°еҠҹиғҪжӯЈзЎ®дёәжӯў гҖӮ

в–І жҺ§еҲ¶еҚ•е…ғеҗҲжҲҗеҗҺзҡ„з»“жһң гҖӮ жңҖеҗҺ пјҢ е°ҶеҗҲжҲҗе®Ңзҡ„зЁӢеәҸд»Јз ҒеҶҚж”ҫе…ҘеҸҰдёҖеҘ— EDA tool пјҢ иҝӣиЎҢз”өи·ҜеёғеұҖдёҺз»•зәҝпјҲPlace And Routeпјү гҖӮ еңЁз»ҸиҝҮдёҚж–ӯзҡ„жЈҖжөӢеҗҺ пјҢ дҫҝдјҡеҪўжҲҗеҰӮдёӢзҡ„з”өи·Ҝеӣҫ гҖӮ еӣҫдёӯеҸҜд»ҘзңӢеҲ°и“қгҖҒзәўгҖҒз»ҝгҖҒй»„зӯүдёҚеҗҢйўңиүІ пјҢ жҜҸз§ҚдёҚеҗҢзҡ„йўңиүІе°ұд»ЈиЎЁзқҖдёҖеј е…үзҪ© гҖӮ иҮідәҺе…үзҪ©з©¶з«ҹиҰҒеҰӮдҪ•иҝҗз”Ёе‘ўпјҹ

в–І еёёз”Ёзҡ„жј”з®—иҠҜзүҮ- FFT иҠҜзүҮ пјҢ е®ҢжҲҗз”өи·ҜеёғеұҖдёҺз»•зәҝзҡ„з»“жһң гҖӮ еұӮеұӮе…үзҪ© пјҢ иҝӯиө·дёҖйў—иҠҜзүҮйҰ–е…Ҳ пјҢ зӣ®еүҚе·Із»ҸзҹҘйҒ“дёҖйў— IC дјҡдә§з”ҹеӨҡеј зҡ„е…үзҪ© пјҢ иҝҷдәӣе…үзҪ©жңүдёҠдёӢеұӮзҡ„еҲҶеҲ« пјҢ жҜҸеұӮжңүеҗ„иҮӘзҡ„д»»еҠЎ гҖӮ дёӢеӣҫдёәз®ҖеҚ•зҡ„е…үзҪ©дҫӢеӯҗ пјҢ д»ҘйӣҶжҲҗз”өи·ҜдёӯжңҖеҹәжң¬зҡ„组件 CMOS дёәиҢғдҫӢ пјҢ CMOS е…ЁеҗҚдёәдә’иЎҘејҸйҮ‘еұһж°§еҢ–зү©еҚҠеҜјдҪ“пјҲComplementary metalвҖ“oxideвҖ“semiconductorпјү пјҢ д№ҹе°ұжҳҜе°Ҷ NMOS е’Ң PMOS дёӨиҖ…еҒҡз»“еҗҲ пјҢ еҪўжҲҗ CMOS гҖӮ иҮідәҺд»Җд№ҲжҳҜйҮ‘еұһж°§еҢ–зү©еҚҠеҜјдҪ“пјҲMOSпјүпјҹиҝҷз§ҚеңЁиҠҜзүҮдёӯе№ҝжіӣдҪҝз”Ёзҡ„组件жҜ”иҫғйҡҫиҜҙжҳҺ пјҢ дёҖиҲ¬иҜ»иҖ…д№ҹиҫғйҡҫеј„жё… пјҢ еңЁиҝҷйҮҢе°ұдёҚеӨҡеҠ з»Ҷ究 гҖӮ дёӢеӣҫдёӯ пјҢ е·Ұиҫ№е°ұжҳҜз»ҸиҝҮз”өи·ҜеёғеұҖдёҺз»•зәҝеҗҺеҪўжҲҗзҡ„з”өи·Ҝеӣҫ пјҢ еңЁеүҚйқўе·Із»ҸзҹҘйҒ“жҜҸз§ҚйўңиүІдҫҝд»ЈиЎЁдёҖеј е…үзҪ© гҖӮ еҸіиҫ№еҲҷжҳҜе°ҶжҜҸеј е…үзҪ©ж‘ҠејҖзҡ„ж ·еӯҗ гҖӮ еҲ¶дҪңжҳҜ пјҢ дҫҝз”ұеә•еұӮејҖе§Ӣ пјҢ дҫқеҫӘдёҠдёҖзҜҮ IC иҠҜзүҮзҡ„еҲ¶йҖ дёӯжүҖжҸҗзҡ„ж–№жі• пјҢ йҖҗеұӮеҲ¶дҪң пјҢ жңҖеҗҺдҫҝдјҡдә§з”ҹжңҹжңӣзҡ„иҠҜзүҮдәҶ гҖӮ гҖҗзәізұі|и®©дҪ жӣҙжё…жҘҡзҡ„дәҶи§Јзәізұіе·ҘиүәгҖҒзЎ…жҷ¶еңҶгҖҒICгҖ‘

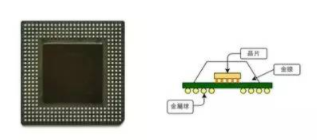

иҮіжӯӨ пјҢ еҜ№дәҺ IC и®ҫи®Ўеә”иҜҘжңүеҲқжӯҘзҡ„дәҶи§Ј пјҢ ж•ҙдҪ“зңӢжқҘе°ұеҫҲжё…жҘҡ IC и®ҫи®ЎжҳҜдёҖй—ЁйқһеёёеӨҚжқӮзҡ„дё“дёҡ пјҢ д№ҹеӨҡдәҸдәҶи®Ўз®—жңәиҫ…еҠ©иҪҜ件зҡ„жҲҗзҶҹ пјҢ и®© IC и®ҫи®Ўеҫ—д»ҘеҠ йҖҹ гҖӮ IC и®ҫи®ЎеҺӮеҚҒеҲҶдҫқиө–е·ҘзЁӢеёҲзҡ„жҷәиғҪ пјҢ иҝҷйҮҢжүҖиҝ°зҡ„жҜҸдёӘжӯҘйӘӨйғҪжңүе…¶дё“й—Ёзҡ„зҹҘиҜҶ пјҢ зҡҶеҸҜзӢ¬з«ӢжҲҗеӨҡй—Ёдё“дёҡзҡ„иҜҫзЁӢ пјҢ еғҸжҳҜж’°еҶҷ硬件жҸҸиҝ°иҜӯиЁҖе°ұдёҚеҚ•зәҜзҡ„еҸӘйңҖиҰҒзҶҹжӮүзЁӢеәҸиҜӯиЁҖ пјҢ иҝҳйңҖиҰҒдәҶи§ЈйҖ»иҫ‘з”өи·ҜжҳҜеҰӮдҪ•иҝҗдҪңгҖҒеҰӮдҪ•е°ҶжүҖйңҖзҡ„з®—жі•иҪ¬жҚўжҲҗзЁӢеәҸгҖҒеҗҲжҲҗиҪҜ件жҳҜеҰӮдҪ•е°ҶзЁӢеәҸиҪ¬жҚўжҲҗйҖ»иҫ‘й—ёзӯүй—®йўҳ гҖӮ еңЁдәҶи§Ј IC и®ҫи®ЎеёҲеҰӮеҗҢе»әзӯ‘еёҲ пјҢ жҷ¶еңҶд»Је·ҘеҺӮжҳҜе»әзӯ‘иҗҘйҖ еҺӮд№ӢеҗҺ пјҢ жҺҘдёӢжқҘиҜҘжҡёи§ЈжңҖз»ҲеҰӮдҪ•жҠҠиҠҜзүҮеҢ…иЈ…жҲҗдёҖиҲ¬з”ЁжҲ·жүҖзҶҹзҹҘзҡ„еӨ–и§Ӯ пјҢ д№ҹе°ұжҳҜгҖҢе°ҒиЈ…гҖҚ гҖӮ дёӢйқўе°Ҷд»Ӣз»Қ IC е°ҒиЈ…жҳҜд»Җд№Ҳд»ҘеҸҠеҮ дёӘйҮҚиҰҒзҡ„жҠҖжңҜ гҖӮ гҖҗеҚҠеҜјдҪ“科жҷ®гҖ‘е°ҒиЈ… пјҢ IC иҠҜзүҮзҡ„жңҖз»ҲйҳІжҠӨдёҺз»ҹж•ҙз»ҸиҝҮжј«й•ҝзҡ„жөҒзЁӢ пјҢ д»Һи®ҫи®ЎеҲ°еҲ¶йҖ пјҢ з»ҲдәҺиҺ·еҫ—дёҖйў— IC иҠҜзүҮдәҶ гҖӮ 然иҖҢдёҖйў—иҠҜзүҮзӣёеҪ“е°Ҹдё”и–„ пјҢ еҰӮжһңдёҚеңЁеӨ–ж–ҪеҠ дҝқжҠӨ пјҢ дјҡиў«иҪ»жҳ“зҡ„еҲ®дјӨжҚҹеқҸ гҖӮ жӯӨеӨ– пјҢ еӣ дёәиҠҜзүҮзҡ„е°әеҜёеҫ®е°Ҹ пјҢ еҰӮжһңдёҚз”ЁдёҖдёӘиҫғеӨ§е°әеҜёзҡ„еӨ–еЈі пјҢ е°ҶдёҚжҳ“д»Ҙдәәе·Ҙе®үзҪ®еңЁз”өи·ҜжқҝдёҠ гҖӮ еӣ жӯӨ пјҢ жң¬ж–ҮжҺҘдёӢжқҘиҰҒй’ҲеҜ№е°ҒиЈ…еҠ д»ҘжҸҸиҝ°д»Ӣз»Қ гҖӮ зӣ®еүҚеёёи§Ғзҡ„е°ҒиЈ…жңүдёӨз§Қ пјҢ дёҖз§ҚжҳҜз”өеҠЁзҺ©е…·еҶ…еёёи§Ғзҡ„ пјҢ й»‘иүІй•ҝеҫ—еғҸиңҲиҡЈзҡ„ DIP е°ҒиЈ… пјҢ еҸҰдёҖдёәиҙӯд№°зӣ’иЈ… CPU ж—¶еёёи§Ғзҡ„ BGA е°ҒиЈ… гҖӮ иҮідәҺе…¶д»–зҡ„е°ҒиЈ…жі• пјҢ иҝҳжңүж—©жңҹ CPU дҪҝз”Ёзҡ„ PGAпјҲPin Grid ArrayпјӣPin Grid ArrayпјүжҲ–жҳҜ DIP зҡ„ж”№иүҜзүҲ QFPпјҲеЎ‘ж–ҷж–№еҪўжүҒе№іе°ҒиЈ…пјүзӯү гҖӮ еӣ дёәжңүеӨӘеӨҡз§Қе°ҒиЈ…жі• пјҢ д»ҘдёӢе°ҶеҜ№ DIP д»ҘеҸҠ BGA е°ҒиЈ…еҒҡд»Ӣз»Қ гҖӮ дј з»ҹе°ҒиЈ… пјҢ еҺҶд№…дёҚиЎ°йҰ–е…ҲиҰҒд»Ӣз»Қзҡ„жҳҜеҸҢжҺ’зӣҙз«ӢејҸе°ҒиЈ…пјҲDual Inline PackageпјӣDIPпјү пјҢ д»ҺдёӢеӣҫеҸҜд»ҘзңӢеҲ°йҮҮз”ЁжӯӨе°ҒиЈ…зҡ„ IC иҠҜзүҮеңЁеҸҢжҺ’жҺҘи„ҡдёӢ пјҢ зңӢиө·жқҘдјҡеғҸжқЎй»‘иүІиңҲиҡЈ пјҢ и®©дәәеҚ°иұЎж·ұеҲ» пјҢ жӯӨе°ҒиЈ…жі•дёәжңҖж—©йҮҮз”Ёзҡ„ IC е°ҒиЈ…жҠҖжңҜ пјҢ е…·жңүжҲҗжң¬дҪҺе»үзҡ„дјҳеҠҝ пјҢ йҖӮеҗҲе°ҸеһӢдё”дёҚйңҖжҺҘеӨӘеӨҡзәҝзҡ„иҠҜзүҮ гҖӮ дҪҶжҳҜ пјҢ еӣ дёәеӨ§еӨҡйҮҮз”Ёзҡ„жҳҜеЎ‘ж–ҷ пјҢ ж•Јзғӯж•Ҳжһңиҫғе·® пјҢ ж— жі•ж»Ўи¶ізҺ°иЎҢй«ҳйҖҹиҠҜзүҮзҡ„иҰҒжұӮ гҖӮ еӣ жӯӨ пјҢ дҪҝз”ЁжӯӨе°ҒиЈ…зҡ„ пјҢ еӨ§еӨҡжҳҜеҺҶд№…дёҚиЎ°зҡ„иҠҜзүҮ пјҢ еҰӮдёӢеӣҫдёӯзҡ„ OP741 пјҢ жҲ–жҳҜеҜ№иҝҗдҪңйҖҹеәҰжІЎйӮЈд№ҲиҰҒжұӮдё”иҠҜзүҮиҫғе°ҸгҖҒжҺҘеӯ”иҫғе°‘зҡ„ IC иҠҜзүҮ гҖӮ

в–І е·Ұеӣҫзҡ„ IC иҠҜзүҮдёә OP741 пјҢ жҳҜеёёи§Ғзҡ„з”өеҺӢж”ҫеӨ§еҷЁ гҖӮ еҸіеӣҫдёәе®ғзҡ„еү–йқўеӣҫ пјҢ иҝҷдёӘе°ҒиЈ…жҳҜд»ҘйҮ‘зәҝе°ҶиҠҜзүҮжҺҘеҲ°йҮ‘еұһжҺҘи„ҡпјҲLeadframeпјү гҖӮ пјҲSource пјҡе·ҰеӣҫWikipediaгҖҒеҸіеӣҫWikipediaпјүиҮідәҺзҗғж јж•°з»„пјҲBall Grid Array пјҢ BGAпјүе°ҒиЈ… пјҢ е’Ң DIP зӣёжҜ”е°ҒиЈ…дҪ“з§Ҝиҫғе°Ҹ пјҢ еҸҜиҪ»жҳ“зҡ„ж”ҫе…ҘдҪ“з§Ҝиҫғе°Ҹзҡ„иЈ…зҪ®дёӯ гҖӮ жӯӨеӨ– пјҢ еӣ дёәжҺҘи„ҡдҪҚеңЁиҠҜзүҮдёӢж–№ пјҢ е’Ң DIP зӣёжҜ” пјҢ еҸҜе®№зәіжӣҙеӨҡзҡ„йҮ‘еұһжҺҘи„ҡ пјҢ зӣёеҪ“йҖӮеҗҲйңҖиҰҒиҫғеӨҡжҺҘзӮ№зҡ„иҠҜзүҮ гҖӮ 然иҖҢ пјҢ йҮҮз”Ёиҝҷз§Қе°ҒиЈ…жі•жҲҗжң¬иҫғй«ҳдё”иҝһжҺҘзҡ„ж–№жі•иҫғеӨҚжқӮ пјҢ еӣ жӯӨеӨ§еӨҡз”ЁеңЁй«ҳеҚ•д»·зҡ„дә§е“ҒдёҠ гҖӮ

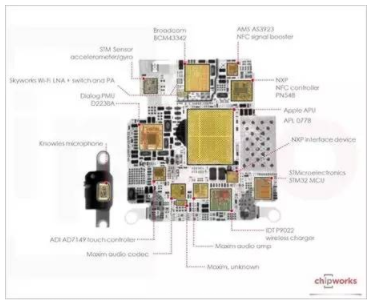

в–І е·ҰеӣҫдёәйҮҮз”Ё BGA е°ҒиЈ…зҡ„иҠҜзүҮ пјҢ дё»жөҒзҡ„ X86 CPU еӨ§еӨҡдҪҝз”Ёиҝҷз§Қе°ҒиЈ…жі• гҖӮ еҸіеӣҫдёәдҪҝз”ЁиҰҶжҷ¶е°ҒиЈ…зҡ„ BGA зӨәж„Ҹеӣҫ гҖӮ пјҲSourceпјҡ е·ҰеӣҫWikipediaпјүиЎҢеҠЁиЈ…зҪ®е…ҙиө· пјҢ ж–°жҠҖжңҜи·ғдёҠиҲһеҸ°з„¶иҖҢ пјҢ дҪҝз”Ёд»ҘдёҠиҝҷдәӣе°ҒиЈ…жі• пјҢ дјҡиҖ—иҙ№жҺүзӣёеҪ“еӨ§зҡ„дҪ“з§Ҝ гҖӮ еғҸзҺ°еңЁзҡ„иЎҢеҠЁиЈ…зҪ®гҖҒз©ҝжҲҙиЈ…зҪ®зӯү пјҢ йңҖиҰҒзӣёеҪ“еӨҡз§Қ组件 пјҢ еҰӮжһңеҗ„дёӘ组件йғҪзӢ¬з«Ӣе°ҒиЈ… пјҢ з»„еҗҲиө·жқҘе°ҶиҖ—иҙ№йқһеёёеӨ§зҡ„з©әй—ҙ пјҢ еӣ жӯӨзӣ®еүҚжңүдёӨз§Қж–№жі• пјҢ еҸҜж»Ўи¶ізј©е°ҸдҪ“з§Ҝзҡ„иҰҒжұӮ пјҢ еҲҶеҲ«дёә SoCпјҲSystem On Chipпјүд»ҘеҸҠ SiPпјҲSystem In Packetпјү гҖӮ еңЁжҷәиғҪеһӢжүӢжңәеҲҡе…ҙиө·ж—¶ пјҢ еңЁеҗ„еӨ§иҙўз»ҸжқӮеҝ—дёҠзҡҶеҸҜеҸ‘зҺ° SoC иҝҷдёӘеҗҚиҜҚ пјҢ 然иҖҢ SoC 究з«ҹжҳҜд»Җд№ҲдёңиҘҝпјҹз®ҖеҚ•жқҘиҜҙ пјҢ е°ұжҳҜе°ҶеҺҹжң¬дёҚеҗҢеҠҹиғҪзҡ„ IC пјҢ ж•ҙеҗҲеңЁдёҖйў—иҠҜзүҮдёӯ гҖӮ и—үз”ұиҝҷдёӘж–№жі• пјҢ дёҚеҚ•еҸҜд»Ҙзј©е°ҸдҪ“з§Ҝ пјҢ иҝҳеҸҜд»Ҙзј©е°ҸдёҚеҗҢ IC й—ҙзҡ„и·қзҰ» пјҢ жҸҗеҚҮиҠҜзүҮзҡ„и®Ўз®—йҖҹеәҰ гҖӮ иҮідәҺеҲ¶дҪңж–№жі• пјҢ дҫҝжҳҜеңЁ IC и®ҫи®Ўж—¶й—ҙж—¶ пјҢ е°Ҷеҗ„дёӘдёҚеҗҢзҡ„ IC ж”ҫеңЁдёҖиө· пјҢ еҶҚйҖҸиҝҮе…ҲеүҚд»Ӣз»Қзҡ„и®ҫи®ЎжөҒзЁӢ пјҢ еҲ¶дҪңжҲҗдёҖеј е…үзҪ© гҖӮ 然иҖҢ пјҢ SoC 并йқһеҸӘжңүдјҳзӮ№ пјҢ иҰҒи®ҫи®ЎдёҖйў— SoC йңҖиҰҒзӣёеҪ“еӨҡзҡ„жҠҖжңҜй…ҚеҗҲ гҖӮ IC иҠҜзүҮеҗ„иҮӘе°ҒиЈ…ж—¶ пјҢ еҗ„жңүе°ҒиЈ…еӨ–йғЁдҝқжҠӨ пјҢ дё” IC дёҺ IC й—ҙзҡ„и·қзҰ»иҫғиҝң пјҢ жҜ”иҫғдёҚдјҡеҸ‘з”ҹдәӨдә’е№Іжү°зҡ„жғ…еҪў гҖӮ дҪҶжҳҜ пјҢ еҪ“е°ҶжүҖжңү IC йғҪеҢ…иЈ…еңЁдёҖиө·ж—¶ пјҢ е°ұжҳҜеҷ©жўҰзҡ„ејҖе§Ӣ гҖӮ IC и®ҫи®ЎеҺӮиҰҒд»ҺеҺҹе…Ҳзҡ„еҚ•зәҜи®ҫи®Ў IC пјҢ еҸҳжҲҗдәҶ解并ж•ҙеҗҲеҗ„дёӘеҠҹиғҪзҡ„ IC пјҢ еўһеҠ е·ҘзЁӢеёҲзҡ„е·ҘдҪңйҮҸ гҖӮ жӯӨеӨ– пјҢ д№ҹдјҡйҒҮеҲ°еҫҲеӨҡзҡ„зҠ¶еҶө пјҢ еғҸжҳҜйҖҡи®ҜиҠҜзүҮзҡ„й«ҳйў‘и®ҜеҸ·еҸҜиғҪдјҡеҪұе“Қе…¶д»–еҠҹиғҪзҡ„ IC зӯүжғ…еҪў гҖӮ жӯӨеӨ– пјҢ SoC иҝҳйңҖиҰҒиҺ·еҫ—е…¶д»–еҺӮе•Ҷзҡ„ IPпјҲintellectual propertyпјүжҺҲжқғ пјҢ жүҚиғҪе°ҶеҲ«дәәи®ҫи®ЎеҘҪзҡ„组件ж”ҫеҲ° SoC дёӯ гҖӮ еӣ дёәеҲ¶дҪң SoC йңҖиҰҒиҺ·еҫ—ж•ҙйў— IC зҡ„и®ҫи®Ўз»ҶиҠӮ пјҢ жүҚиғҪеҒҡжҲҗе®Ңж•ҙзҡ„е…үзҪ© пјҢ иҝҷеҗҢж—¶д№ҹеўһеҠ дәҶ SoC зҡ„и®ҫи®ЎжҲҗжң¬ гҖӮ жҲ–и®ёдјҡжңүдәәиҙЁз–‘дҪ•дёҚиҮӘе·ұи®ҫи®ЎдёҖйў—е°ұеҘҪдәҶе‘ўпјҹеӣ дёәи®ҫи®Ўеҗ„з§Қ IC йңҖиҰҒеӨ§йҮҸе’ҢиҜҘ IC зӣёе…ізҡ„зҹҘиҜҶ пјҢ еҸӘжңүеғҸ Apple иҝҷж ·еӨҡйҮ‘зҡ„дјҒдёҡ пјҢ жүҚжңүйў„з®—иғҪд»Һеҗ„зҹҘеҗҚдјҒдёҡжҢ–и§’йЎ¶е°–е·ҘзЁӢеёҲ пјҢ д»Ҙи®ҫи®ЎдёҖйў—е…Ёж–°зҡ„ IC пјҢ йҖҸиҝҮеҗҲдҪңжҺҲжқғиҝҳжҳҜжҜ”иҮӘиЎҢз ”еҸ‘еҲ’з®—еӨҡдәҶ гҖӮ жҠҳиЎ·ж–№жЎҲ пјҢ SiP зҺ°иә«дҪңдёәжӣҝд»Јж–№жЎҲ пјҢ SiP и·ғдёҠж•ҙеҗҲиҠҜзүҮзҡ„иҲһеҸ° гҖӮ е’Ң SoC дёҚеҗҢ пјҢ е®ғжҳҜиҙӯд№°еҗ„家зҡ„ IC пјҢ еңЁжңҖеҗҺдёҖж¬Ўе°ҒиЈ…иҝҷдәӣ IC пјҢ еҰӮжӯӨдҫҝе°‘дәҶ IP жҺҲжқғиҝҷдёҖжӯҘ пјҢ еӨ§е№…еҮҸе°‘и®ҫи®ЎжҲҗжң¬ гҖӮ жӯӨеӨ– пјҢ еӣ дёәе®ғ们жҳҜеҗ„иҮӘзӢ¬з«Ӣзҡ„ IC пјҢ еҪјжӯӨзҡ„е№Іжү°зЁӢеәҰеӨ§е№…дёӢйҷҚ гҖӮ

в–І Apple Watch йҮҮз”Ё SiP жҠҖжңҜе°Ҷж•ҙдёӘи®Ўз®—жңәжһ¶жһ„е°ҒиЈ…жҲҗдёҖйў—иҠҜзүҮ пјҢ дёҚеҚ•ж»Ўи¶іжңҹжңӣзҡ„ж•ҲиғҪиҝҳзј©е°ҸдҪ“з§Ҝ пјҢ и®©жүӢиЎЁжңүжӣҙеӨҡзҡ„з©әй—ҙж”ҫз”өжұ гҖӮ пјҲSourceпјҡApple е®ҳзҪ‘пјүйҮҮз”Ё SiP жҠҖжңҜзҡ„дә§е“Ғ пјҢ жңҖи‘—еҗҚзҡ„йқһ Apple Watch иҺ«еұһ гҖӮ еӣ дёә Watch зҡ„еҶ…йғЁз©әй—ҙеӨӘе°Ҹ пјҢ е®ғж— жі•йҮҮз”Ёдј з»ҹзҡ„жҠҖжңҜ пјҢ SoC зҡ„и®ҫи®ЎжҲҗжң¬еҸҲеӨӘй«ҳ пјҢ SiP жҲҗдәҶйҰ–иҰҒд№ӢйҖү гҖӮ и—үз”ұ SiP жҠҖжңҜ пјҢ дёҚеҚ•еҸҜзј©е°ҸдҪ“з§Ҝ пјҢ иҝҳеҸҜжӢүиҝ‘еҗ„дёӘ IC й—ҙзҡ„и·қзҰ» пјҢ жҲҗдёәеҸҜиЎҢзҡ„жҠҳиЎ·ж–№жЎҲ гҖӮ дёӢеӣҫдҫҝжҳҜ Apple Watch иҠҜзүҮзҡ„з»“жһ„еӣҫ пјҢ еҸҜд»ҘзңӢеҲ°зӣёеҪ“еӨҡзҡ„ IC еҢ…еҗ«еңЁе…¶дёӯ гҖӮв–І Apple Watch дёӯйҮҮз”Ё SiP е°ҒиЈ…зҡ„ S1 иҠҜзүҮеҶ…йғЁй…ҚзҪ®еӣҫ гҖӮ пјҲSourceпјҡchipworksпјү

е®ҢжҲҗе°ҒиЈ…еҗҺ пјҢ дҫҝиҰҒиҝӣе…ҘжөӢиҜ•зҡ„йҳ¶ж®ө пјҢ еңЁиҝҷдёӘйҳ¶ж®өдҫҝиҰҒзЎ®и®Өе°ҒиЈ…е®Ңзҡ„ IC жҳҜеҗҰжңүжӯЈеёёзҡ„иҝҗдҪң пјҢ жӯЈзЎ®ж— иҜҜд№ӢеҗҺдҫҝеҸҜеҮәиҙ§з»ҷз»„иЈ…еҺӮ пјҢ еҒҡжҲҗжҲ‘们жүҖи§Ғзҡ„з”өеӯҗдә§е“Ғ гҖӮ иҮіжӯӨ пјҢ еҚҠеҜјдҪ“дә§дёҡдҫҝе®ҢжҲҗдәҶж•ҙдёӘз”ҹдә§зҡ„д»»еҠЎ гҖӮ

жҺЁиҚҗйҳ…иҜ»

- зқЎзң |ж–°з ”з©¶пјҡйҷӨдәҶзҶ¬еӨңпјҢзқЎеҫ—еӨӘж—©д№ҹдјҡеҪұе“ҚеҜҝе‘ҪпјҢ50еІҒд»ҘдёҠжӣҙеә”еӨҡжіЁж„Ҹ

- жҳҘеӨ©пјҢиҰҒеӨҡеҗғиҝҷиӮүпјҢжҜ”зҢӘиӮүдҫҝе®ңжҜ”зҫҠиӮүжё©е’ҢпјҢиҗҘе…»ж»ӢиЎҘжӣҙи§ЈйҰӢ

- 全家йғҪзҲұжӯӨз”ңзӮ№пјҢйҰҷз”ңй…ҘиҪҜжҳ“дәҺж¶ҲеҢ–пјҢе°‘жІ№е°‘зі–еҒҡжі•з®ҖеҚ•жӣҙи§ЈйҰӢ

- зү№зҲұеҗғзҡ„еҮ йҒ“家常иҸңпјҢиҪ»жқҫжӢҝдёӢпјҢи®©дҪ з§’еҸҳеӨ§еҺЁпјҒеҘҪеҗғеҸҲдёӢйҘӯиҗҘе…»

- зі–е°ҝ病并еҸ‘з—Ү|зі–е°ҝз—…дәәзҡ„иғ–дёҺзҳҰпјҢе“ӘдёӘжӣҙе®№жҳ“еҸ‘з”ҹ并еҸ‘з—Үпјҹ

- ж—©йӨҗпјҢжҲ‘家йҡ”дёүе·®дә”еҗғжұӨйқўпјҢжңүиҸңжңүжұӨејҖиғғеҠ©ж¶ҲеҢ–пјҢжҜ”зІҘжӣҙиҗҘе…»

- жҺҘз§Қз–«иӢ—|专家пјҡжҺҘз§Қз–«иӢ—дҪҝдё–з•ҢеҸҳеҫ—жӣҙеҠ зҫҺеҘҪ

- йҘәеӯҗйҰ…жӢҢеҘҪеҲ«зқҖжҖҘеҢ…пјҢеӨҡеҒҡдёҖжӯҘпјҢжӣҙйҰҷпјҢжӣҙеҘҪеҗғпјҒдёҖеӨ§й”…дёҚеӨҹеҗғ

- зәўзғ§йёЎзҝ…ж—¶пјҢеӨҡеҠ дёҖдёӘжӯҘйӘӨпјҢйёЎзҝ…жӣҙе…Ҙе‘іпјҢиҖҢдё”жІЎи…Ҙе‘і

- иҘҝи‘«иҠҰеҲ«еҶҚзӮ’зқҖеҗғдәҶпјҢеҒҡжҲҗйҰ…йҘјжӣҙиҗҘе…»пјҢеҘҪеҗғиҝҳдёҚиҙөпјҢз®ҖеҚ•еҸҲжҳ“еҒҡпјҒ