台积电|台积电进一步扩大产能,2nm晶圆厂和封装工厂正在筹备中

文章图片

文章图片

文章图片

全球最大的半导体合同制造商台积电对N2(2nm)制造工艺节点充满信心 , 它已经在考虑建造一个额外的晶圆厂来满足它 。 据报道 , 台积电计划建立两个用于先进芯片封装的工厂 。 #台积电2022年大规模量产3nm芯片#

台积电的N2:计划一个晶圆厂 , 考虑另一个

正式而言 , 台积电的N2工艺仍处于寻路和研究模式 , 因为代工厂正在研究材料以及可行的晶体管结构 。 在上个月的技术研讨会上台积电透漏 , N2开发和初始生产的所在地将是该公司在新竹县宝山附近的生产基地 。 目前 , 台积电正在完成其新的R1研发设施的建设 , 该设施最初将专注于N2 , 并将于明年开始运营 。 台积电的首批2nm芯片将在一个新的晶圆厂中生产 , 该晶圆厂将分四个阶段进行 。 目前 , 该公司正在为晶圆厂收购土地 。

如果新的晶圆厂N2宝山附近提供的容量不足以满足需求 , 那么台积电将考虑建另一个领先的生产设备 。

场效应管

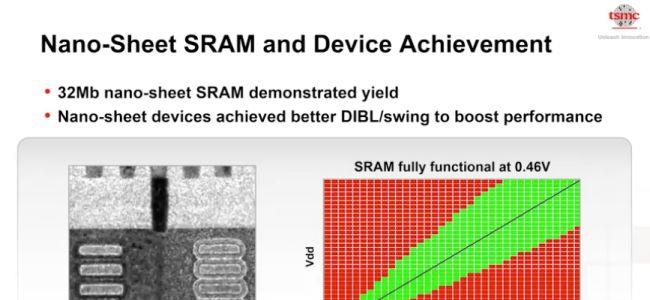

人们普遍认为 , 台积电将为其N2工艺节点采用全栅(GAAFET)晶体管结构(即纳米线 , 纳米带等) 。 该公司已经对GAAFET进行了15年的研究 , 并且最近展示了工作在0.46V电压下的32Mb纳米片SRAM原型 , 因此GAA是最有可能用于N2的晶体管技术 。

转换为新的晶体管结构不仅对台积电来说非常重要 , 而且对合作伙伴和客户也很重要 。

Cadence和Synopsys等公司将不得不创建全新的电子设计自动化(EDA)工具堆栈 , 并开发全新的IP库 。 芯片开发人员将必须采用全新的设计规则和流程 , 并重新制作他们以前可能从头使用过的所有内容 。 还有一点是 , 就像在2014年至2015年转向FinFET结构一样 , 增加芯片设计成本的同时 , 采用GAAFET可能会再次增加设计成本 。

台积电尚未公开其N2节点的时间表 。 该公司上个月透露 , 它将在2022年下半年开始使用基于FinFET的N3工艺技术开始批量生产 。 由于台积电通常每年都会引入一个新节点以满足其大型客户的需求 , 因此合乎逻辑的是 , 在2023年 , 它将使用N3的改进版本(例如N3+ , N3P等) , 或开始使用其N2 。 无论如何 , 台积电的2nm技术至少要三年 。

新的高级包装设施已在计划中

就研发、生产和芯片设计而言 , 现代的先进工艺技术极其复杂且昂贵 。 同时 , 它们并不总是像十年或两年前那样提供显着的节点到节点扩展和收益 。 为此 , 在许多情况下 , 开发使用领先技术的大型单片芯片以获得一定水平的性能和某些功能并不是最佳选择 。

相反 , 采用小芯片设计并使用最合适的过程生产每个小芯片是有意义的 。 小芯片集成需要先进的2.5D封装和3D堆叠技术 , 并且近年来对这些技术的需求预计会迅速增长 。

台积电拥有许多先进的2.5D封装和3D硅堆叠技术 , 统称为3DFabric 。 台积电的逻辑上逻辑堆叠CoW(晶片上晶片)和WoW(晶片上晶片)技术需要先进的前端生产设备 , 而基于中介层的封装方法如CoWoS(晶片上晶片)以及诸如InFO(集成扇出)之类的堆叠式封装互连都使用后端fab技术 。

虽然逻辑上的逻辑集成比CoWoS或InFO之类的内在复杂且昂贵 , 但是所有类型的3DFabric都需要洁净室空间 , 并且这种包装设施与典型的测试和包装工厂相去甚远 。 为了使事情变得更加复杂 , 具有多个小芯片的高级处理器将同时使用3D堆栈和2.5D封装 , 因此下一代封装设施必须同时支持后端和前端技术 。

目前 , 台积电拥有四个先进的包装设施 。 台积电预计在未来几年内对其3DFabric服务的需求将会强劲 , 因此它准备再建两个新的封装设施 , 这些设施将提供前端3D堆叠以及后端CoWoS和InFO封装过程 。

其中一个晶圆厂将位于新竹科学园的春安区 。 据报道 , 该晶圆厂全部建成并配备完毕后 , 其成本将高达101.1亿美元 , 它可能是业内最昂贵的测试和包装设备 。 预计该晶圆厂将于2021年下半年上线 。

另一个晶圆厂将位于科学园区 , 预计将于2022年某个时候开始量产 。

【台积电|台积电进一步扩大产能,2nm晶圆厂和封装工厂正在筹备中】想了解更多精彩内容 , 快来关注互联范儿

推荐阅读

- 3道电饭煲版懒人焖饭,饭菜一锅出,满嘴喷香,美味省心~!

- 液态金属|脑科学日报:开发用于活体神经记录的可拉伸液态金属电极阵列

- 1碗面粉2个鸡蛋,教您做电饭锅面包,一看就会,简单好吃零失手

- 整只鸡丢电饭锅里,不放油不加水,出锅香味四溢还流油,比烤鸡香

- 教你1碗面粉4个鸡蛋做蛋糕,不用烤箱不用电饭煲,新手一次成功

- 电休克|电休克用于儿童青少年患者的疗效及安全性|研究简报

- 电饭煲做蛋糕,方法是关键,轻松做出8厘米高度,蓬松暄软又细腻

- 马也|马也会“鸭梨山大”!兽用脑电波判断你的宠物快乐吗?

- 叶片|又创世界纪录,世界最长风电叶片在江苏盐城下线

- 在家自制面包,不用烤箱,电饭锅就搞定,比馒头软,学会不用买了